### National Exams December 2010

#### 07-Elec-A4, Digital Systems & Computers

#### 3 hours duration

### **NOTES:**

- 1. If doubt exists as to the interpretation of any question, the candidate is urged to submit with the answer paper, a clear statement of any assumptions made.

- 2. This is a Closed Book exam.

Candidates may use one of two calculators, the Casio or Sharp approved models.

- 3. FIVE (5) questions constitute a complete exam.

You are required to answer questions 1, 2, 4 and 6.

You have a choice of answering question 3 or question 5.

- Questions 1, 2, 4 and 6 are worth 12 points.

Questions 3 and 5 are worth 16 points.

For a detailed breakdown see marking scheme on next page.

## **Marking Scheme**

- 1. (a) 3, (b) 3, (c) 3, (d) 3, total = 12

- 2. (a) 9, (b) 3, total = 12

- 3. (a) 2, (b) 3, (c) 5, (d) 3, (e) 3, total = 16

- 4. (a) 3, (b) 3, (c) 3, (d) 3, total = 12

- 5. (a) 6, (b) 6, (c) 4, total = 16

- 6. (a) 3, (b) 3, (c) 3, (d) 3, total = 12

The number beside each part above indicates the points that part is worth

1.- Given the following function in sum of products form:

$$f(A, B, C) = A \cdot B \cdot \overline{C} + B \cdot C + A \cdot \overline{B} \cdot C$$

- (a) Prepare its truth table. [3 pts]

- (b) Express f in canonical product of sums form. [3 pts]

- (c) Use Karnaugh maps (K-maps) to express f in minimized product of sums form. [3 pts]

- (d) Synthesize a NOR-only circuit for f with a minimum number of gates. [3 pts]

- 2.- A circuit is needed to start and stop counting clock pulses on command.

- (a) Design a 3-bit synchronous counter that goes through the sequence 000, 001, 010, 011, 100, 101, 110 and then repeats. Use positive-edge-triggered JK flip-flops. Label the bits Q<sub>C</sub>, Q<sub>B</sub> & Q<sub>A</sub> where Q<sub>C</sub> is the most significant bit. Draw the circuit implementing the counter.

- (b) Modify the circuit so that it counts whenever an additional COUNT ENABLE (CTE) input is HIGH, stops counting when CTE goes LOW and resumes counting from where it stopped when CTE goes HIGH again. [3 pts]

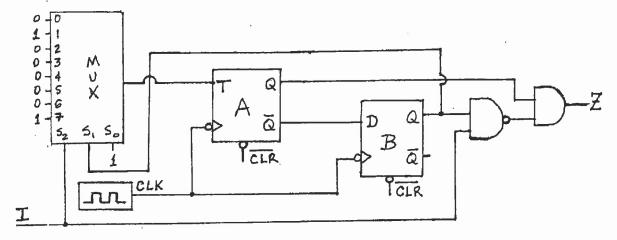

- 3.- The finite state machine (FSM) shown in the figure below is implemented with one toggle (T) flip-flop and one D flip-flip. It has a single input I and a single output Z. The combinational logic required is implemented by an 8:1 MUX, 1 NAND and 1 AND gates.

- (a) Is this a Moore or a Mealy FSM? Justify.

[2 pts]

(b) Write the logic expressions for  $T_A$ ,  $D_B$  and Z.

[3 pts]

(c) Obtain the state transition table including  $T_A$ ,  $D_B$ ,  $Q_A^+$ ,  $Q_B^+$  and the output Z.

[5 pts]

(d) Draw the state transition diagram of the FSM including input I and output Z values.

[3 pts]

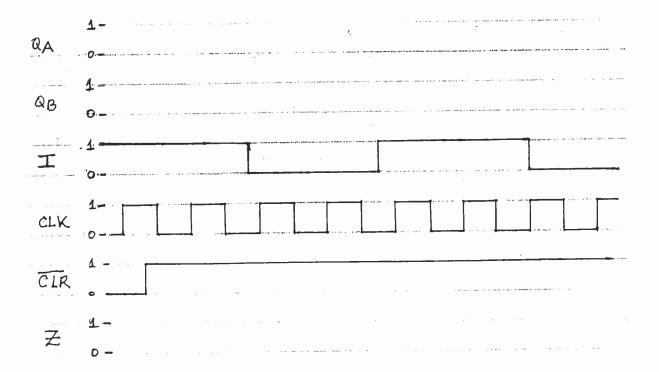

(e) Assuming that the preset input  $\overline{PR}$  is not asserted fill the timing diagram below for  $Q_A$ ,  $Q_B$  and Z. [3 pts]

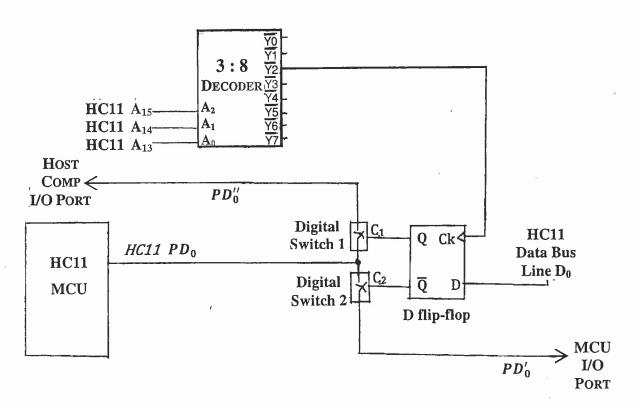

4.- The diagram below shows the use of a D flip-flop governing two digital switches in order to route line PD<sub>0</sub> of the HC11 microcontroller unit (MCU) to one of two connectors: the HOST computer I/O port or the MCU I/O port connector.

Digitals switches close when control input C is at a logic '1' and remain open when C is '0'. HC11 address lines  $A_{15}$  -  $A_{13}$  are connected to the 3 address inputs of a 3:8 decoder as shown in the figure, the most significant address input of the decoder is  $A_2$  and the least significant is  $A_0$ . Assume the decoder is enabled and towards the end of the execution of each instruction cycle all its active-low inputs  $\overline{Y}_0$  -  $\overline{Y}_7$  go back to their inactive logic '1' state. The least significant data bus line of the HC11 ( $D_0$ ) is connected to the flip-flop D input. Knowing that instruction

ldaa #\$xx means load HC11 CPU register accumulator A with hexadecimal value xx, and staa \$zzzz means store the value in accumulator A to address \$zzzz,

which of the following set of instructions will direct HC11 line  $PD_0$  to the HOST computer I/O port, which to the MCU I/O port connector and which will not affect the current routing. Mark your choice with an X and justify your selection in each case.

| (a) | ldaa #\$10, staa \$8000 | [ ] HOST Comp I/O port, | [ ] MCU I/O port, | [] No Action  |

|-----|-------------------------|-------------------------|-------------------|---------------|

| (b) | ldaa #\$29, staa \$4000 | [ ] HOST Comp I/O port, | [ ] MCU I/O port, | [ ] No Action |

| (c) | ldaa #\$B4, staa \$5000 | [ ] HOST Comp I/O port, | [ ] MCU I/O port, | [ ] No Action |

| (d) | ldaa #\$05. staa \$2500 | [ ] HOST Comp I/O port, | [ ] MCU I/O port, | [ ] No Action |

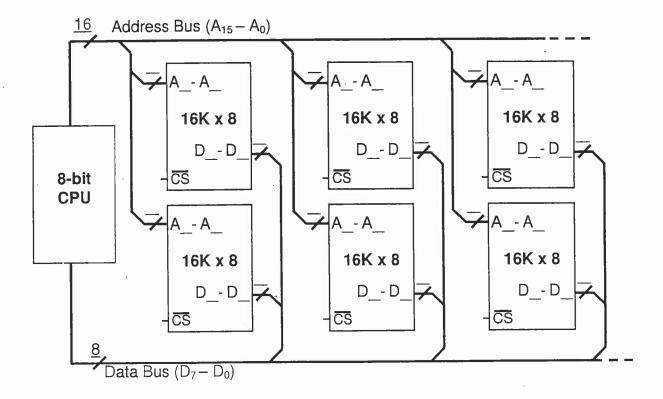

- 5.- Provide this 8-bit CPU with a 64Kbyte memory space by making use of 16K x 8 memory chips like the ones provided in the figure below.

- (a) Fill in the blanks *beside* and *inside* the memory chips with the appropriate numbers. The number on top of this symbol represents the number of lines on that bus. The spaces besides the A's and the D's are to indicate which lines of the address and data busses are connected to each chip, respectively.

[6 pts]

(b) Complete the connections in the figure below adding logic gates where needed to produce the chip select  $(\overline{CS})$  signals needed in the decoding logic. Explain the reasons for the connections made, include expressions for the Boolean logic used.

[6 pts]

(c) Provide the address range allocated to each of the chips used.

[4 pts]

Note:  $R/\overline{W}$  & clock signals are omitted for simplicity.

[3 pts]

| 6 | (a) | Mention the three basic logic gates.  Is it possible to realize any combinational logic function using just one type of gate? |  |  |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------|--|--|

|   |     | Explain. [3 pts]                                                                                                              |  |  |

|   |     |                                                                                                                               |  |  |

|   |     |                                                                                                                               |  |  |

|   |     |                                                                                                                               |  |  |

|   |     |                                                                                                                               |  |  |

|   | (b) | What is the main difference between combinational and sequential circuits? [3 pts]                                            |  |  |

|   |     |                                                                                                                               |  |  |

|   |     |                                                                                                                               |  |  |

|   |     |                                                                                                                               |  |  |

|   |     |                                                                                                                               |  |  |

|   | (c) | What is a finite state machine (FSM)?                                                                                         |  |  |

|   |     | Is a counter a special case of FSM? Explain. [3 pts]                                                                          |  |  |

|   |     |                                                                                                                               |  |  |

|   |     |                                                                                                                               |  |  |

|   |     |                                                                                                                               |  |  |

|   |     |                                                                                                                               |  |  |

(d) Mention the difference between synchronous and asynchronous counters. How would you identify one type or the other?

# **Excitation Table**

| Q | Q+ | R | S   | J | K | T | D   |   |

|---|----|---|-----|---|---|---|-----|---|

| 0 | 0  | X | 0   | 0 | X | 0 | 0   |   |

| 0 | 1  | 0 | 1   | 1 | X | 1 | . 1 |   |

| 1 | 0  | 1 | 0   | X | 1 | 1 | 0   | . |

| 1 | 1  | 0 | - X | X | 0 | 0 | 1   |   |

# Basic Boolean Identities

|                   | Identity                                                                                                                     | Comments                                                   |

|-------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 1.<br>2.          | A + 0 = A $A + 1 = 1$                                                                                                        | Operations with 0 and 1 Operations with 0 and 1 Idompotent |

| 3.<br>4.          | $A + A = A$ $A + \overline{A} = 1$                                                                                           | Complementarity                                            |

| 5.<br>6.          | $A \cdot 0 = 0$<br>$A \cdot 1 = A$                                                                                           | Operations with 0 and 1 Operations with 0 and 1            |

| 7.<br>8.          | $ \begin{array}{l} A \cdot A = A \\ A \cdot \overline{A} = 0 \end{array} $                                                   | Idompotent Complementarity                                 |

| 9.<br><b>10</b> . | $\overline{A} = A$ $A + B = B + A$                                                                                           | Involution Commutative                                     |

| 11.<br>12.        | $A \cdot B = B \cdot A$<br>A + (B + C) = (A + B) + C = A + B + C                                                             | Commutative<br>Associative                                 |

| 13.<br>14.        | $A \cdot (B \cdot C) = (A \cdot B) \cdot C = A \cdot B \cdot C$<br>$A \cdot (B + C) = (A \cdot B) + (A \cdot C)$             | Associative Distributive                                   |

| 15.<br>16.        | $A + (B \cdot C) = (A + B) \cdot (A + C)$<br>$A + (A \cdot B) = A$                                                           | Distributive Absorption                                    |

| 17.<br>18.        | $A \cdot (A + B) = A$<br>$(A \cdot B) + (\overline{A} \cdot C) + (B \cdot C) = (A \cdot B) + (\overline{A} \cdot C)$         | Absorption<br>Consensus                                    |

| 19.               | $\overline{A+B+C+} = \overline{A} \cdot \overline{B} \cdot \overline{C} \cdot$                                               | De Morgan                                                  |

| 20.<br>21.        | $\overline{A \cdot B \cdot C \cdot} = \overline{A} + \overline{B} + \overline{C} +$ $(A + \overline{B}) \cdot B = A \cdot B$ | De Morgan<br>Simplification                                |

| 22.               | $(A \cdot \overline{B}) + B = A + B$                                                                                         | Simplification                                             |